任何高安全要求的系统归根到底都会有半导体集成电路(IC)的存在。例如,用于控制传感器上有运行控制逻辑的IC,传感器本身也是基于IC实现。IC在最后阶段驱动某个器件达到安全状态。另外,IC也是运行软件的平台。半导体内部的高集成度可以简化系统级实现,集成度越高,部件数量越少,诊断测试之间的间隔越短。换句话说,可以通过有限的成本来提高安全性。一些人认为增加集成度是不可取的,因为它增加了复杂性。然而,在模块和系统级别,复杂性换来了相当大的简化。生产过程控制、机械、电梯、变速驱动器和有毒气体传感器都有相应的功能安全标准,但关于集成电路却没有专门的功能安全标准。相关要求和知识是零散地分布在IEC 61508和其他一些衍生的标准中,比如新版的ISO26262第11部分。

简介

通常,集成电路按照IEC 61508或ISO 26262标准进行开发。另外,二级和三级标准中有时还会有其他要求。按照功能安全标准进行开发和评估,可以用于检验日趋复杂的IC是安全的。当初编写IEC 61508时,其针对的是定制系统,而不是开放市场批量生产的集成电路。本文将回顾并评论集成电路的已知功能安全要求。对于ISO26262等标准中增加的半导体部分应用,目前刚刚发布并,但实际上,半导体公司已经在执行一些安全标准,本文通过讨论既往基于IEC 61508及其在工业领域的应用的案例,给各位一些参考。

功能安全

所谓功能安全,顾名思义,是安全性的一部分。着眼于可靠性,用于评估系统在需要的时候是否有执行安全相关的任务。功能安全不同于其他被动形式的安全,如电气安全、机械安全或本质安全。

功能安全是一种主动形式的安全。例如,它能确保马达以足够快的速度关闭,防止对驾驶员造成伤害,或者当有人在附近时,会降低运行的速度和力度。

标准

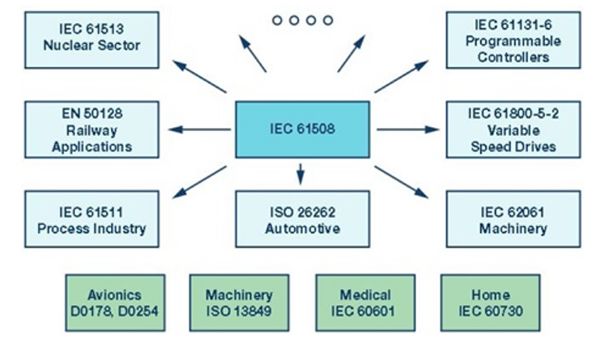

最初的功能安全标准是IEC 61508 1。该标准的第一版于1998年出版,第二版于2010年出版,并于2017年开始更新至第三版的工作,可能的完成日期是在 2022 年。自从 1998 年公布 IEC 61508 第一版以来,基本IEC 61508 标准已针对不同领域进行适应性修改,例如汽车 (ISO 26262)、过程控制(IEC 61511)、PLC(IEC 61131-6)、IEC 62061 (机械)、变速驱动器(IEC 61800-5-2)以及其他许多领域。此类标准有助于对非常宽泛的IEC 61508进行解释以便用于这些受到更大限制的领域。

一些功能安全标准,例如ISO 13849和D0-178/D0-254,并非衍生自 IEC 61508。尽管如此,任何熟悉IEC 61508并阅读这些标准的人都不会对其内容感到过于吃惊。

在安全系统内,当系统运行时,执行关键功能安全活动的是安全功能。安全功能定义了实现或保持安全所必须执行的操作。典型的安全功能包含输入子系统、逻辑子系统和输出子系统。通常,这意味着对潜在的不安全状态进行检测,并且基于检测到的值做出决定,如果认为有潜在危险,则指示输出子系统将系统置于已定义的安全状态。

图1 功能安全示例

不安全状态存在到到达安全状态的时间至关重要。例如,安全功能可能包括如下部分:一个传感器用来检测防护装置是否打开,一个MCU用来处理数据,以及一个具有动力输入关闭的变速驱动器,它在插入机器中的手可能接近运动部件之前关闭电机。

安全完整性等级

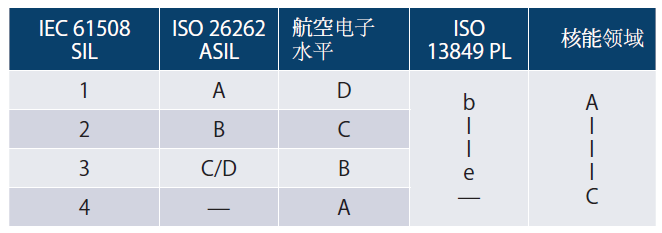

SIL代表安全完整性等级,是表示需要将风险降至何种程度才能达到可接受水平的手段。根据IEC 61508标准,安全等级有1~4四级,从一个级别到下一个级别,安全性会提高一个数量级。机器和工厂自动化场景中不会看到 SIL 4,因为一般情况下,这种场合中遭受危险的人员通常不会超过一个。SIL 4 针对的是数百甚至数千人可能受到伤害的核能和铁路等应用。还有其他功能安全标准,例如汽车使用 ASIL(汽车安全完整性等级) A、B、C 和 D,以及 ISO 13849 标准。其性能等级 a、b、c、d 和 e 可以对应到 SIL 1 至 SIL 3 尺度。

表 1.各应用领域安全等级的粗略对应

笔者不相信单个 IC 可能有超过 SIL 3 的安全水平。但值得注意的是,IEC 61508-2:2010 附录 F 中的表格显示了一个 SIL 4 的列。

三项关键要求

功能安全对IC开发提出了三项关键要求。下面研究这些要求。

要求1:严格的遵循开发流程

功能安全标准是一个全生命周期模型,涵盖了从安全概念到需求收集、维护,直至最终物料处理的所有阶段。不是所有这些阶段都与集成电路相关,甄别哪些阶段有关需要培训和经验(点击阅读原文,了解牛喀网功能安全最佳实践培训)。比如IEC 61508为ASIC提供了一个V模型,另外还有审查、审核及其他要求,它代表了一个体系,虽然不能保证安全,但过去已证明它能产安全的系统和IC。

由于更改故障集成电路的成本很高,所以大多数 IC 制造商已经建立严格的新产品开发标准。对于小几何尺寸工艺,仅仅一套掩膜的成本就可能超过50万美元。这种情况加上长交货期,迫使集成电路设计商不得不实施严格的开发流程和优良的检查与验证阶段。功能安全的一大区别在于,不仅必须实现安全性,还要证明安全性,即使是最好的IC制造商也需要在其正常开发流程之上添加安全流程,以确保合规性的适当证据得以创建并存档 。

开发流程引入的故障称为系统故障。这些故障只能通过设计变更来解决。与需求收集相关的故障、EMC鲁棒性不足和测试不充分就是此类故障。

IEC 61508-2:2010的附录F列出了一系列专门测量,IEC委员会专家认为这些测量适合用于集成电路开发。表F.2适用于FPGA和CPLD,表F.1适用于数字ASIC。这些测量分为R(推荐)或HR(强烈推荐类,具体取决于 SII,某些情况下还提供了备选技术。对于拥有良好开发流程的IC供应商来说,其中的要求很少会让人感到意外,但SIL 3的99%故障覆盖率要求是有挑战性的,尤其是对于小型数字或混合信号器件,其中很多电路位于模块的外围。该标准第二版中的要求仅适用于数字IC,但许多要求也可应用于模拟或混合信号IC。

除表F.1和表F.2外,还有一些介绍性文字也提供了一些见解。例如,这个介绍性文字说允许使用经过实际验证的工具,在复杂度相似的项目中使用18个月是合理的时间长度。这意味着并不需要应用IEC 61508-3关于工具的全部要求。

如果模块/系统设计者过去曾成功使用某一 IC,并且了解其应用和现场故障率,那么他可以宣称其“经过实际验证”。对于集成电路设计者或制造商来说,作出这种宣称要困难得多,因为他们一般不太了解最终应用或将现场故障单元返回给他们进行分析的百分率的含义 。

软件

所有软件错误都是系统性的,因为软件不会老化。通常,片内软件可能包括微控制器/ DSP 的内核/引导程序。但在某些情况下,微控制器/DSP 可能包含一个由IC制造商预编程的小型微控制器来实现一个逻辑块,而不是使用状态机。该预编程的微控制器软件还需要符合软件部分的要求。应用级软件通常是模块/系统设计者的责任,而不是IC制造商的责任,但IC供应商可能需要提供编译器或低级驱动程序等工具。如果这些工具用于安全相关应用软件的开发,那么IC制造商需要为最终用户提供足够的信息,以满足标准对工具的要求。

笔者也使用C语言和其他很多编程语言做过编程。笔者还做过少量 Verilog 编程。Verilog 及其语言VHDL是用于设计数字集成电路的两种代表性硬件定义语言 (HDL)。有趣的是,HDL是否是软件?欢迎大家在留言区讨论。一个值得注意的相关标准是 IEC 62566 2,它处理的是利用HDL开发的核工业安全功能。

要求2:确保本质可靠

标准以PFH(单位时间内平均危险故障频率)或PFD(作动时发生故障的概率)的形式提出了可靠性要求。这些限制与成年人因自然原因而死亡的概率,在工作或处理日常业务时不应显著增加这一想法有关。比如IEC 61508中SIL 3安全功能的最大PFH为10–7/h,或者每1000年约有一次的危险故障率。表示为FIT(故障次数/每运行十亿小时的故障率)的话,即为100 FIT。

鉴于典型的安全功能有一个输入模块、一个逻辑模块和一个执行器模块,并且 PFH 预算必须分配给所有三个模块,所以某一IC的PFH可能必须限制到个位数(不到10 FIT)。可以使用冗余架构来提高这些数字,若有两个100FIT结构,每个可以提供相同的置信度,可以达到一个10FIT器件等同的可靠性(受共因失效(CCF)限制)。然而,冗余会增加面积、功耗和成本。

IC制造商会在网站上提供其所有已发布 IC的基于加速老化测试的可靠性信息。此信息有时会不被重视,因为这种可靠性评估是在人工创造的条件下于实验室中完成的。业界广泛推荐使用SN295003或IEC 623804这些标准,但这些标准有一些问题:

• 预测99%置信度下的可靠性,和IEC 61508仅要求70%置信度下的数据相比,偏悲观。

• 将随机故障模式和系统故障模式混为一谈。

• 不是经常更新。

• 不允许不同供应商之间的质量差异。

SN 29500之类的标准说明的是片内晶体管的可靠性。如果使用两个IC (每个有 50 万个晶体管)来实现安全功能,如果整个系统的FIT为140,那么,每个 IC的FIT为70。但是,如果用一个含100万个晶体管的IC来替代这两个IC,那么这一个IC的FIT只有80,减少了40%以上。

IC内部的软错误往往被忽略。软错误不同于传统的可靠性预测,因为一旦断电再通电,软错误就会消失。引起软错误的原因是空间中的中子或封装材料中的α粒子,它们撞击片内RAM单元或触发器(FF),改变其中存储的值。ECC(双比特错误检测和单比特错误校正)可用来检测并无缝纠正 RAM 中的错误,但代价是速度降低和片内错误增多。奇偶校验增加的开销更少,但系统设计人员需要解决错误恢复问题。如果不使用奇偶校验或 ECC 技术,则软错误率可能会比传统硬错误率高出多达1000倍 (IEC 61508 提供的RAM数值为 1000 FIT/MB)。用于解决实现逻辑电路的FF (触发器)中软错误的技术不那么令人满意,但看门狗定时器、时间冗余以及其他技术可提供帮助。

要求3:容错性

无论产品有多可靠,有时候还是会出事。容错性承认这一现实并予以解决。容错性主要包含两方面。一个是使用冗余,另一个是使用诊断。这两方面都承认,无论IC的可靠性或IC开发流程有多好,故障难免会发生。

冗余可以是相同的或不同的,可以在片内或片外。IEC 61508-2:2010 的附录 E 提供了一组技术来证明,已经采取了充分的措施来支持关于数字电路使用相同冗余的片内冗余性声明。附录E似乎是针对双锁步微控制器的,针对以下方面的片内独立性没有给出任何指导:

• 模拟和混合信号集成电路

• 芯片上的器件及其片内诊断功能

• 采用异构型冗余的数字电路

可以针对某些场景对附录E进行合理的解释。附录 E 中有一个有意思的内容是 βIC 计算,其衡量片内共因失效。如果代表共因失效的来源的 β 小于 25%,则认为是充分分解的。这与 IEC 61508-6:2010 的表格中的 1%、5% 或 10% 相比是较高的。

诊断是集成电路真正可以大放异彩的领域。片内诊断可以:

• 根据片内每个模块的预期故障模式进行设计

• 仅使用少量外部引脚,PCB 面积不会显著增大

• 高速率运行(诊断测试间隔极小 )

• 器件冗余的必要性下降

这意味着片内诊断可以最大限度地减少系统成本和面积。通常,诊断功能与片上监控完全独立的实现。因此,减少了与监视目标同时发生故障的可能性。尽管诊断功能是独立实现的,如果诊断功能与监视功能同时发生相同的故障时,多数情况下,我们考虑是与EMC、电源和温度过高有关的问题。虽然该标准不包含此要求,但对片内电源监视器和看门狗电路仍然存在担心,而这些是最后的诊断手段。某些外部评估人员会坚持将此类诊断放在片外。

一般来说,对较简单集成电路的诊断将由远程微控制器/DSP 控制,测量在片内完成,但结果发送到芯片外进行处理。

标准要求最低级别的诊断覆盖率,用SFF(安全失效系数)给出,其考虑安全故障和危险故障,与忽略安全故障的DC(诊断覆盖率)相关但不同。已实施诊断的程度可以使用量化FMEA或FMEDA来衡量。但是,在 IC 中实施的诊断也可以覆盖IC外部的器件,IC内的器件通过系统级诊断来覆盖的情况也存在。当IC开发人员执行FMEDA时,必须假定IC开发人员不知道最终应用的细节 。在ISO 26262术语中,这被称为SEooC(脱离背景的安全要素)。用户必须确信上述假设对其系统成立,才能使用IC级的FMEDA数据。

虽然 IEC 61508-2:2010的表 A.1 (实际上是表 A.2 至 A.14)就 IC 失效提供了很好的指导,分析IC时应予以考虑,但IEC 60730:2010 5的附录 H 就该主题提供了更好的论述。

集成电路开发方案

开发用于功能安全系统的集成电路有几种方案。标准中没有要求只能使用符合标准的集成电路,而是要求模块或系统设计人员要确认所选的集成电路适用于目标系统。

可用方案包括:

方案 1:利用外部评估机构,参考安全手册,按照标准进行开发

方案 2:不用外部评估机构,参考安全手册,按照标准进行开发

方案 3:按照公开安全datasheet的半导体公司的标准开发流程进行开发

方案 4:按照半导体企业的标准流程进行开发

注意:未依照标准开发的器件,其安全手册可能被称为安全datasheet或类似名称,以避免与遵照安全手册开发的器件发生混淆。

对于半导体制造商来说,方案1成本最高,但对模块或系统设计商来说可能最有利。IC安全概念中显示的应用与系统的应用相匹配,可以降低模块或系统进行外部机构评估时遇到问题的风险。SIL 2安全功能的额外设计工作量可能在 20% 或更多。即使没有功能安全,半导体制造商通常也已经实施了严格的开发流程。如果没有导入这样的开发流程,可能需要一些额外的补充工作。

方案2节省了外部评估的成本,但其他方面和方案1相同。如果客户要进行模块/系统级别的认证,并且集成电路是该系统的重要组成部分,那么此方案是合适的。

方案3最适合于已经发布的集成电路,提供安全数据手册可以让模块或系统设计人员获得其在更高级别上进行安全设计所需的额外信息。这包括如下信息:所用实际开发流程的详细信息,集成电路的 FIT 数据,所有诊断的详细信息,以及制造现场的 ISO 9001 认证结果等。

然而,方案4仍然是开发集成电路最常用的方法。使用此类器件开发安全模块或系统,需要额外的器件和开支,因为这些器件可能采用的是单通道的架构,通过双通道架构的比较来实现的诊断功能没有完备,必须做补充额外的措施。因为没有安全数据手册,模块/系统设计人员要基于保守的假设,将集成电路视为黑盒子。

此外,半导体公司需要制定自己对标准的解释。

SIL 2/3 开发

也有按照SIL 3的所有系统性要求进行IC开发的情况,IEC 61508-2:2010 表F.1包含了所有相关要求。这意味着所有设计评审和其他分析都按照SIL 3级要求完成。但是,有些情况下,硬件量化标准只能满足SIL 2的要求,这种电路可以被标识为SIL 2/3或更典型的SIL M/N,其中M表示根据硬件量化标准可以声明的最高SIL级别,N表示根据系统性要求可以声明的最高SIL级别。两个SIL 2/3 集成电路可用来实现SIL 3模块或系统,因为根据硬件量化标准,两个SIL 2器件并联就会将该组合升级到SIL 3,而就系统性要求而言,每个器件都已经是SIL 3。如果集成电路仅是SIL 2/2,那么即使将两个这样的集成电路并联也充其量是SIL 3/2,不会达到SIL 3。

将硬件量化标准应用于IC

除非全部安全功能都由集成电路实现,否则很难为半导体指定 SFF、DC或PFH限值。以SFF为例,SIL 3要求SFF大于99%,这是全部安全功能,而不只是集成电路。SFF为98%的集成电路,可以用于SIL 3 的安全功能,但系统的其他部分需要实现更高的覆盖率以进行补偿。集成电路的安全手册或安全datasheet需要公布 λDD、λDU 和 λ 等系统级 FMEDA计算使用的参数。

理想情况下,IC要求是在系统级分析中导出的,但通常情况并非如此,开发实际上是一个SEooC(参见ISO 26262,脱离背景的安全要素)。在 SEooC 的情况下,IC开发者需要假设IC在系统中将会如何使用。然后,系统或模块设计者必须将这些假设与实际系统进行比较,以确定IC的功能安全性对系统是否足够。这些假设可以决定诊断是在IC上实施,还是在系统级实施,并因此影响到IC级特性和功能。

信息安全(Security)

信息安全对系统的安全性也十分重要。此前,IEC 61508 或 ISO 26262 中与信息安全有关的指导只有“参考 IEC 62443 系列 6“。但是,IEC 62443 似乎更多地是针对较大的组件,例如整个PLC组件,而不是单个IC。好消息是,功能安全标准中消除系统故障的大部分要求也适用于信息安全。没有任何参照是很有趣的,根据硬件的不同,可以出现诸如硬件信任根(root of trust)和类似PUF (物理上不可复制的功能)的功能,PUF对于安全和信息安全的意义非常重要。

结论

安全标准涵盖了从集成电路开发到炼油厂的一切。还有针对汽车、过程控制等领域有专门的行业专用标准,IEC 61508第二版中也有关于集成电路的一些指导,但可以自由的进行各种解释,不同客户和外部评估人员的期望之间可能出现不一致。

这意味着,各行业将倾向于按照更高层次的标准对集成电路提出行业特定的要求。这样的要求已经可以在EN 50402 7 等标准中看到,但最特别的是 ISO 26262的2018版中,新增的第11部分专门处理集成电路。但由于标准刚刚发布,大家在导入过程中可以借鉴的经验较少,遇到的问题也越来越多。